Race Around Condition in JK Flip flop

When both J and K input of a JK Flip flop is set to 1, the output of the JK flip-flop will toggle between 1 and 0, which make the output of the flip-flop unstable. This is called the race-around condition in a JK Flipflop. to avoid this problem, we use the concept of a master-slave JK flip flop.

Design of Master Slave JK Flip flop

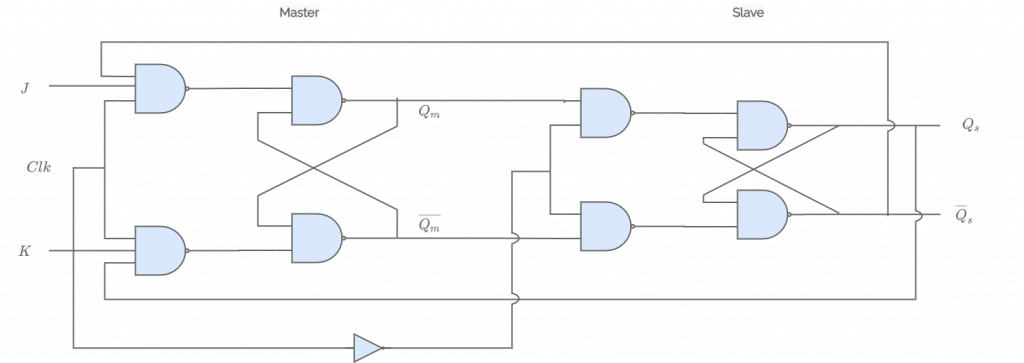

A Master-Slave JK Flip-Flop is designed by connecting two JK flip-flops in a series configuration. In these one flip-flop act as the master and the other as a slave. The output of the master flip-flop is connected to both the inputs of the slave flip-flop. Also, the outputs of the slave flip-flop are fed back to inputs of the master flip-flop. Block diagram of a master-slave JK flipflop is shown in the figure.

The circuit also includes an inverter and is connected. It passes the inverted clock pulse to the slave flip-flop. If the clock pulse is set to 0 for the master, then the clock pulse will become 1 for the slave and if Clk=1 for the master flipflop, it will become 0 for the slave flipflop. The circuit diagram of a master-slave Jk Flip flop is given below.

Working of Master Slave JK Flip flop

The slave flip-flop is isolated until the Clk goes to 0. When the Clk goes to 0, values are passed from the master flip-flop to the slave and output is obtained.

If and

,

output of the master becomes 1 which is then transferred to the K input of the slave and the clock forces the slave to RESET, thus the slave flip-flop copies the master flip-flop.

If and

,

output of the master becomes 1 and goes to the J input of the slave and the clock sets the slave, copying the master.

If both and

, the master toggles on the positive transition of the clock and the slave toggles on the negative transition of the clock.

If J=0 and K=0, Q remains unchanged.

Timing Diagram of Master Slave JK Flip flop