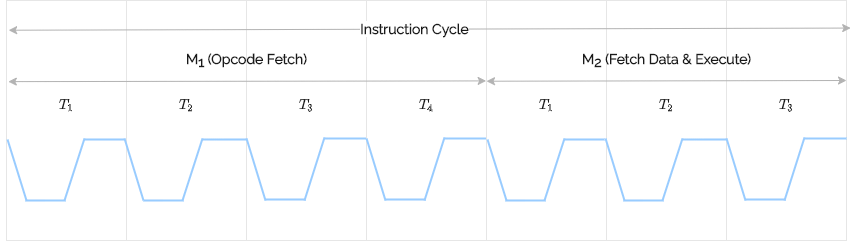

The timing diagram is a graphical representation of the process in steps with respect to time. It represents the step by step working of each instruction and its execution. The execution time of instructions is represented in T-states.

Machine Cycle– The time required to access the memory or input/output device is called the machine cycle.

T-states– The portion of an operation carried out in one clock period is called a T-state. A t-state is defined as the time elapsed between the falling edge of one clock pulse and the falling edge of the next clock pulse.

Instruction Cycle

The time required to complete the execution of an instruction is called an instruction cycle. It may consist of one or more machine cycles. The first of these is always the opcode fetch cycle. The following steps should be performed to execute an instruction.

- Fetch – The address stored in the program counter (PC) is used to fetch the next instruction, which is then stored in the instruction register.

- Decode – The encoded instruction from the instruction register is interpreted by the decoder.

- Reading effective address – The address specified in the instruction is read from main memory, and the required data is fetched. The effective address is determined by whether direct or indirect addressing is used.

- Execute – Consists of memory read (MR), memory write (MW), input output read (IOR) and input output write (IOW).

The fetch cycle takes 4 t-states and the execution cycle takes 3 t-states. A typical instruction cycle and the machine cycles within it is shown in the figure.

Opcode Fetch Machine Cycle

Every instruction’s first machine cycle is an opcode fetch machine cycle, during which the 8085 microprocessor determines the type of instruction to be executed. During this machine cycle, the processor puts the contents of the programme counter to the address lines and reads the instruction’s opcode through the read process. The following figures show the timing diagram for the opcode fetch machine cycle.

The number of states in the opcode fetch machine cycle may vary from 4T states to 6T states as per the instruction. The following is a detailed step-by-step explanation of the opcode fetch cycle.

State T1

- Places the contents of PC on the address bus.

- The higher order bits(PCH) is placed on the A15-A8 lines.

- The lower order bts(PCL) is placed on the AD7-AD0 lines.

- ALE signal goes high in the beginning to indicate that AD7-AD0 contains lower address bits.

- The status signals

specifies whether it is a memory or I/O operation.

- The

status signal specifies whether it is read/write operation.

- In opcode fetch machine cycles status signals are:

.

State T2

- The lower order address disappears from the AD7-AD0 lines.

- The

signal is set to 0 to enable the addressed memory location.

- The contents of addressed memory location is placed on the databus (AD7-AD0).

State T3

- The opcode is loaded into the instruction register from the databus.

- The

is raised to 1 which disables the memory device.

State T4

- Decodes the opcode.

- One byte instructions that operate on 8bit data are executed in T4.

Memory Read Machine Cycle

During the memory read machine cycle, the contents of a memory location are read. This machine cycle is made up of three T states. The first three T states are almost the same as the first three T states of the Opcode Fetch Machine Cycle. The following figures show the timing diagram for the memory read machine cycle.

The number of states in the opcode fetch machine cycle may vary from 4T states to 6T states as per the instruction. The following is a detailed step-by-step explanation of the memory read machine cycle.

State T1

- Higher address bits have been loaded into A8-A15.

- Lower address bits have been loaded into AD0-AD7.

- In the beginning, the ALE signal is high, indicating that AD0-AD7 includes lower address bits.

goes low since it is a memory operation.

and

become 1 and 0, signifying a Memory Read Machine Cycle.

- By the end of the first T state, ALE goes low. Lower address bits should be latched by this time.

State T2 and T3

goes low, indicating that the read process takes place.

- Data is read from memory and placed onto the data bus AD0-AD7.

- The data is loaded into the data bus at the start of the T2 state and remains in place until the end of the T3 state.

gets high at the end of the T3 state, signifying the end of the read operation.

Memory Write Machine Cycle

Contents are written to a memory location/stack during a memory write machine cycle. This machine cycle is made up of three T states. The following figures show the timing diagram for the memory write machine cycle.

The following is a detailed step-by-step explanation of the memory write machine cycle.

State T1

- Higher address bits have been loaded into A8-A15.

- Lower address bits have been loaded into AD0-AD7.

- In the beginning, the ALE signal is high, indicating that AD0-AD7 includes lower address bits.

goes low since it is a memory operation.

and

become 0 and 1, signifying a Memory Write Machine Cycle.

- By the end of the first T state, ALE goes low. Lower address bits should be latched by this time.

State T2 and T3

goes low, indicating that the write process has begun.

- Data to be written is loaded onto the data bus at the start of the T2 state and remains on the data bus until the end of the T3 state.

- WR goes high at the end of the T3 state, signifying the end of the write operation.